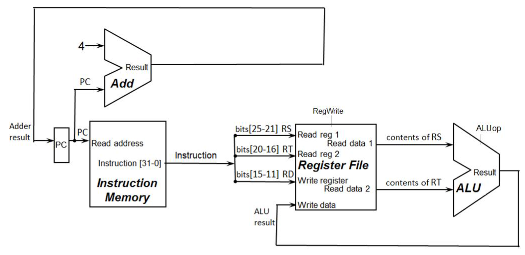

Building a MIPS Single Cycle Datapath - Part 1: R-type Instructions

Abstract

Prior to this activity, students should have already learned how to translate HLL statements into MIPS assembly language, and how to translate MIPS assembly language into MIPS machine language. They should have also learned about individual components within a CPU (program counter, register files, adders, shifters, ALUs, etc).

This activity will guide the students to understand how various CPU components are used by an R-type instruction in the MIPS single cycle CPU datapath.

After completing this activity, learners should be able to: Trace a MIPS R-type instruction through a single cycle CPU datapath, identify the inputs and outputs of each hardware unit, and determine the number of clock cycles required to execute an instruction.

Level: Undergraduate

Setting: Classroom

Discipline: Computer Science

Keywords: CPU datapath, MIPS, single cycle datapath, instruction execution in hardware

Downloads

Published

How to Cite

Issue

Section

License

Copyright of this work and the permissions granted to users of the PAC are defined in the PAC Activity User License.