Building a MIPS Single Cycle Datapath - Part 1: R-type Instructions

Computer Architecture

Abstract

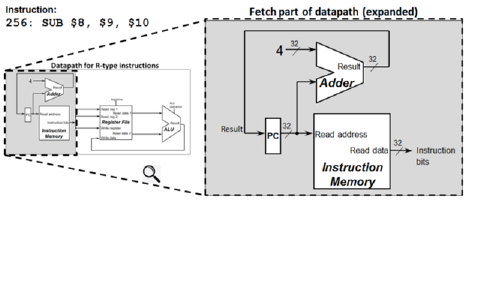

The activity was designed for use in a Computer Organization & Architecture course that uses MIPS assembly language. Prior to this activity, students will have learned about all the individual pieces of hardware that are used to execute instructions. This activity will walk students through the actions performed by each part of the single cycle datapath for MIPS R-type instructions and show the hardware used. An ADD instruction will be used as the R-type instruction example. Each model in the activity will focus on one part of the fetch-decode-execute cycle. The last model will examine the complete datapath, including all parts.

After completing this activity, students should be able to:

- Identify all hardware units that will be used within the CPU, when executing MIPS R-type instructions.

- Describe the datapath that the bits of a MIPS R-type instruction will take when executing on a single cycle CPU, identifying the inputs and outputs of each hardware unit along the way.

- Identify some MIPS instructions that will not be supported by this datapath.

This activity was developed with NSF support through IUSE-1626765. You may request access to this activity via the following link: IntroCS-POGIL Activity Writing Program.

- Level: Undergraduate

- Setting: Classroom

- Activity Type: Application

- Discipline: Computer Science

- Course: Computer Architecture

- Keywords: datapath, single cycle, MIPS single cycle datapath, R-type instruction datapath

Downloads

Published

How to Cite

Issue

Section

License

Copyright of this work and the permissions granted to users of the PAC are defined in the PAC Activity User License.